This product is obsolete.

This information is available for your convenience only.

For more information on Zarlink's obsolete products and replacement product lists, please visit

http://products.zarlink.com/obsolete\_products/

# **ADVANCE INFORMATION**

DS3138-2.1

# MV6001

# HDLC/DMA CONTROLLER

The MV6001 is a combined HDLC transceiver and DMA controller capable of providing serial communications at rates up to 128K bits/second, and handling direct memory access clock rates up to 8MHz.

GEC PLESSEY

SEMICONDUCTORS

## FEATURES

- Data Rates up to 128K Bits/s

- DMA Rate up to 8MHz

- Low Power CMOS

- Simple Interfacing to Popular 8-Bit Processors

- Frame Length up to 2K Bytes

- Low Host-Processor Overhead

- Conforms to ECMA40 and Related Standards (CCITT X25, X75, 1.440, ISO3309, ANSI X3.66, FED-STD 1003, FIPS71)

## **APPLICATIONS**

- ISDN Terminals

- LANs

- X25 p.s.s. Networks

## **ORDERING INFORMATION**

MV6001 B0 DP (Commercial Plastic DIP) MV6001 B0 DG (Commercial Ceramic DIP)

|                                      | $\overline{\bigcirc}$ |                     |

|--------------------------------------|-----------------------|---------------------|

| GND 🗌 1                              |                       | 40 V <sub>CC</sub>  |

| A <sub>0</sub> 🗌 2                   |                       | 39 🗌 MRD            |

| A <sub>1</sub> 🗌 3                   |                       | 38 🗌 MWR            |

| A <sub>2</sub> 4                     |                       | 37 🗌 MR             |

| A <sub>3</sub> 🗌 5                   |                       | 36 🛛 BRQ            |

| A <sub>4</sub> 🗌 6                   |                       | 35 🗌 ВАК            |

| A <sub>5</sub> [] 7                  |                       | 34 🛛 CS             |

| A <sub>6</sub> 🗌 8                   |                       |                     |

| A <sub>7</sub> 🗌 9                   | MUCOOA                | 32 🛛 RD             |

| GND 🗌 10                             | MV6001                | 31 🗌 WR             |

| TST 🗌 11                             |                       |                     |

| A <sub>8</sub> /D <sub>0</sub> [] 12 |                       | 29 TX <sub>OP</sub> |

| A <sub>9</sub> /D <sub>1</sub> 13    |                       | 28 Т <sub>СК</sub>  |

| A <sub>10</sub> /D <sub>2</sub> 14   |                       | 27 R <sub>CK</sub>  |

| A <sub>11</sub> /D <sub>3</sub> 15   |                       | 26 RX <sub>IP</sub> |

| A <sub>12</sub> /D <sub>4</sub> 🗌 16 |                       | 25 AEN              |

| A <sub>13</sub> /D <sub>5</sub> 🗌 17 |                       | 24 ASB              |

| A <sub>14</sub> /D <sub>6</sub> 🗌 18 |                       | 23 R <sub>INT</sub> |

| A <sub>15</sub> /D <sub>7</sub> 🗌 19 |                       | 22 T <sub>INT</sub> |

| GND 🗌 20                             |                       | 21 T <sub>OP2</sub> |

|                                      |                       | DP40<br>DG40        |

Figure 1: Pin connections - top view

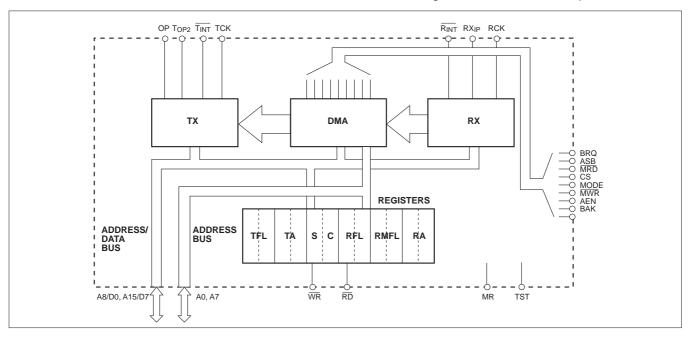

Figure 2: Block diagram

# **PIN DESCRIPTION**

| Pin No. | Name                                                             | I/O | Function                                                                                                                                                                                                                                             |

|---------|------------------------------------------------------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1,10,20 | GND                                                              |     | <b>0V supply</b> . All 3 pins must be connected.                                                                                                                                                                                                     |

| 2 - 9   | A <sub>0</sub> - A <sub>7</sub>                                  | I/O | Address Bus. Output for memory $A_0 - A_7$ addressing. Input for register addresses $A_0$ - $A_3$ .                                                                                                                                                  |

| 11      | TST                                                              | I   | Test Enable. Tie to GND for normal operation.                                                                                                                                                                                                        |

| 12-19   | A <sub>8</sub> /D <sub>0</sub> - A <sub>15</sub> /D <sub>7</sub> | I/O | Data Bus/High Order Address. Multiplexed data and address bus.                                                                                                                                                                                       |

| 21      | TOP2                                                             | 0   | <b>Transmitter Out</b> . Alternative output to TX <sub>OP</sub> . This output is not affected by loop back (see Operating Notes - LOOPBACK).                                                                                                         |

| 22      | ⊤ <sub>int</sub>                                                 | 0   | <b>Transmitter Interrupt</b> . An interrupt is generated whenever transmission of a frame is ended, either following the last FCS byte of a complete frame of when an abort sequence is transmitted. The interrupt is reset by the control register. |

| 23      | $\overline{R}_{INT}$                                             | 0   | <b>Receiver Interrupt</b> . An interrupt is generated whenever a frame is received. The interrupt is reset by the counter register.                                                                                                                  |

| 24      | ASB                                                              | 0   | Address Strobe. Strobes the Address High byte from the Data/Address Bus into an external latch.                                                                                                                                                      |

| 25      | AEN                                                              | 0   | Address Enable. Enables the external address latch.                                                                                                                                                                                                  |

| 26      | RX <sub>IP</sub>                                                 | I   | Receiver Input. Serial HDLC data input, clocked in by RCK.                                                                                                                                                                                           |

| 27      | RCK                                                              | Ι   | <b>Receiver Data Clock</b> . Provides clock to the receiver section, frequency should be at the required data rate, this need not necessarily the the same as the transmit data rate.                                                                |

| 28      | ТСК                                                              | I   | <b>Transmitter Data Clock</b> . This input provides a clock signal for the transmitter section and should be set to the desired transmit data rate.                                                                                                  |

| 29      | TX <sub>OP</sub>                                                 | 0   | Transmitter output. Main transmitter output for serial data.                                                                                                                                                                                         |

| 30      | MODE                                                             | Ι   | <b>Bus Control Mode Select</b> . Controls the polarity of BAK and BRQ.<br>MODE = $V_{CC}$ gives active LOW, MODE = GND gives active HIGH.                                                                                                            |

| 31      | WR                                                               | I   | Write Register. Loads data from data bus into register addressed by $A_0$ - $A_3$ .                                                                                                                                                                  |

| 32      | RD                                                               | I   | Read Register. Reads addressed register onto data bus                                                                                                                                                                                                |

| 33      | DMACK                                                            | I   | <b>DMA Clock.</b> This input provides clock to the DMA section. The DMA clock rate should be at least ten times the sum of the transmit and receive data rates.                                                                                      |

| 34      | CS                                                               | I   | Chip Select. Enables $\overline{RD}$ and $\overline{WR}$ inputs.                                                                                                                                                                                     |

| 35      | BAK                                                              | I   | <b>Bus Acknowledge</b> . Input from processor relinquishing control of bus. See pin 30, Bus Mode Select.                                                                                                                                             |

| 36      | BRQ                                                              | 0   | <b>Bus Request</b> . Output to processor requesting the bus for a DMA cycle. See pin 30, Bus Mode Select.                                                                                                                                            |

| 37      | MR                                                               | Ι   | Master Reset. Resets everything.                                                                                                                                                                                                                     |

| 38      | MWR                                                              | 0   | <b>Memory Write</b> . This is a three-state output to write data into memory during DMA cycles.                                                                                                                                                      |

| 39      | MRD                                                              | 0   | Memory Read. 3-state output to read data from memory during DMA cycles.                                                                                                                                                                              |

| 40      | V <sub>CC</sub>                                                  |     | $\pm$ 5V $\pm$ 10% supply.                                                                                                                                                                                                                           |

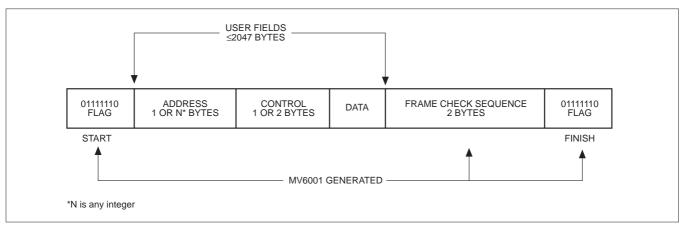

Fig.3 shows the construction of an HDLC frame. The start and finish of the frame are determined by FLAGS (the binary pattern 01111110). To prevent spurious recognition of flags in the user fields, the transmitter automatically inserts a '0' after five successive '1 's. The inserted '0's are removed by the receiver, and hence are not seen by the user. Each HDLC frame contains a 2 byte frame check sequence produced by a cyclic redundancy generator in the transmitter. This sequence is checked by the receiver to validate the frame.

There are two other sequences which have specific meanings - IDLE and ABORT. The IDLE state is the transmission of at least 15 continuous '1's without inserted zeros. ABORT is 7 to 14 consecutive '1's without inserted zeros sandwiched between two zeros.

#### **FUNCTIONAL DESCRIPTION**

The MV6001 consists of four main sections; transmitter, receiver, DMA unit and register bank. Each of the transminer~ receiver and DMA unit have their own clocks running at the required data rates. There are no restrictions on the relative timing between transmit and receive clocks, the DMA clock rate should be greater than ten times the sum of the transmit and receive clock rates.

#### TRANSMISSION

In its steady state the transmitter produces a continuous stream of FLAGS until the control register is loaded with a transmit instruction. The transmitter then, at intervals, requests the DMA unit to fetch a byte of data. This is then transferred from the system memory via the data bus to the transmitter. (If the DMA unit should fail to fetch a byte of data by the time the next request arrives then an under-run will occur and the transmitter will transmit an ABORT sequence). Data is converted into a serial stream with inserted zeros after five ones, and the 16-bit frame check sequence is appended at the end of each frame. As soon as the last bit of the FCS has been clocked out, the TINT OUtPUt goes low to inform the processor that transmission has ended.

#### INITIALISATION

To start transmission, two items of information are required - the start address for the data to be transmitted, and the length of the user fields are loaded into the TA and TFL registers respectively, after which the transmit enable bit (D0) can be set

at any time to start transmission. Once a transmission has been started, the only way it can by stopped is to set the abort bit (D1). The transmitter will then transmit the abort sequence followed by flags. Transmitter reset (D2) resets the transmitter interrupt TINT, clears the TA and TFL registers and bits D0 and D1 of the status register. Transmitter reset is disabled during a transmission.

#### INTERRUPT

A transmitter interrupt  $(\overline{TINT})$  is generated whenever a transmission ceases, the status register can then be read to check if the frame was aborted or not. The interrupt is reset by writing a transmitter reset to the control register. NB. The status register must be read before a transmitter reset as this will alter the contents of the status register.

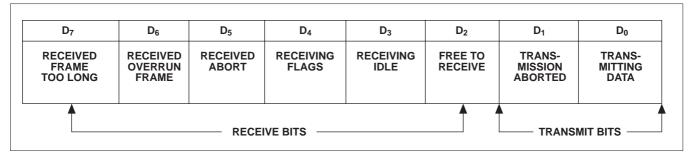

#### STATUS

The transmitter has two status bits - transmitting data (Do) and abort (D1) The transmitting data bit should always be low after  $\overline{T}_{\text{INT}}$  signifying that transmission is ended. The abort bit will be high whenever a frame is aborted either by an abort instruction to the control register, or internally due to an underrun .

#### RECEPTION

The receiver accepts serial data, removes inserted zeros and checks the frame check sequence. For each byte of data received, the receiver section generates a DMA request to transfer the data to memory. If the DMA controller fails to make the transfer before the next request from the receiver, then the receiver will drop out and give a receiver. interrupt with the code in the status register for overrun. If the number of bytes received reaches the number in the receive maximum frame length registerthe receiverwilldropoutand give an interrupt with the code in the status register for frame too long.

#### **INITIALISATION**

The RA register (2 bytes) is loaded with the address where the first received byte of data is to be stored. The RMFL register (11 bits) is loaded with the maximum number of bytes in the user fields plus 3 bytes (+2 bytes for the FCS, +1 byte because an interrupt will occur when the frame length is equal to the length set by the number in the register).

#### CONTROL

The receiver has two control bits in the control register, receive enable (D3) and receive reset (D4). Once the RA and RMFL registers have been loaded, the receive enable bit can be set at any time to allow the receiver to receive a frame. Once set, the receive enable bit cannot be overwritten and receive reset is disabled until a frame has been received.

Receiver reset will reset the  $\overline{R_{INT}}$  interrupt bit, registers RFL, RMFL, RA and bits D2 - D7 of the status register.

#### INTERRUPT

A receive interrupt ( $R_{INT}$ ) is generated whenever a frame is received. The status register can then be read to check the status of the received frame. The interrupt is reset by writing a receiver reset to the control register. Since the reset will clear the receiver bits in the status register, the register must be read before writing the reset to the control register.

#### **STATUS**

The receiver uses bits D2 - D7 of the status register (see Figs. 5 and 6). A valid frame is indicated by both 'overrun' (D6) and 'frame too long' (D7) bits being high. Following  $\overline{R}_{\rm INT}$  the 'free to receive' bit (D2) should be low, indicating that a frame has been received. The abort, overrun and long frame bits will be set according to the state of the frame received. The flag (D4) and idle (D3) bits monitor the incoming signal continuously even when the receiver is disabled.

#### FRAME LENGTH REGISTER

Having received a frame and read the status register, the received frame length can be read from the RFL register. The frame length is given as an eleven bit number and includes the

2 FCS bytes in the count. The register should be read before a receiver reset.

#### LOOPBACK

Bit D7 of the control register, the loopback bit is provided for testing purposes. When the bit is set high an internal connection is made between the transmitter output and receiver input. The main transmitter output ( $TX_{OP}$ ) transmits IDLE (transmitted data is always available on  $T_{OP2}$ ). The receiver is clocked from TCK. The loopback bit will respond to every write to the control register.

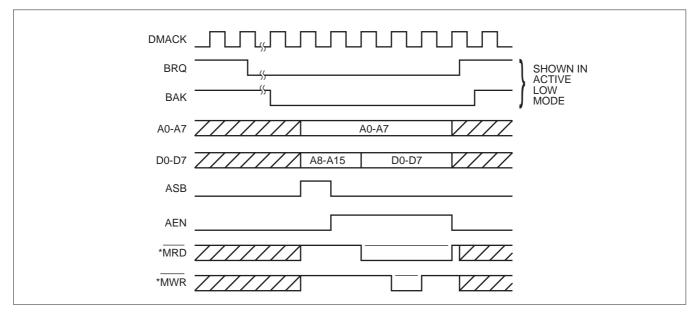

#### **DIRECT MEMORY ACCESS (FIG.11)**

All data transfers to or from memory are carried out by the DMA controller. Each time it receives a request from the transmitter or receiver it will carry out one DMA cycle, i.e. only one byte is transferred at a time. Clashes between transmitter and receiver are resolved in favour of the receiver, otherwise operation is on a first come, first served basis.

#### REGISTERS

Fig.7 shows the addresses for the various instruction and status registers. All registers are readable from and writable to except for S, C and RFL. The S and C registers have the same address, which one is accessed is determined by whether a read (status) or write (control) operation is carried out. Transmitter registers should not be written to when transmitting (except to ABORT a frame), likewise receiver registers should not be written to when receiving. The TA and RA registers update continuously during transmission and reception respectively, giving the next address to be read from or written to.

| D7       | D <sub>6</sub> | D <sub>5</sub> | D4      | D3      | D <sub>2</sub> | <b>D</b> 1 | D <sub>0</sub> |

|----------|----------------|----------------|---------|---------|----------------|------------|----------------|

| LOOPBACK | DON'T          | DON'T          | RECEIVE | RECEIVE | TRANSMIT       | TRANSMIT   | TRANSMIT       |

| ENABLE   | CARE           | CARE           | RESET   | ENABLE  | RESET          | ABORT      | ENABLE         |

Figure 4: Control register

Figure 5: Status register

| Status Register |    |    |    |    |    |    |    |                                                                              |

|-----------------|----|----|----|----|----|----|----|------------------------------------------------------------------------------|

| D7              | D6 | D5 | D4 | D3 | D2 | D1 | D0 | Condition                                                                    |

| Х               | Х  | Х  | Х  | Х  | Х  | 0  | 1  | Currently transmitting data                                                  |

| Х               | Х  | Х  | Х  | Х  | Х  | 0  | 0  | Transmitter disabled, transmission COMPLETE (status read after an interrupt) |

| Х               | х  | Х  | Х  | Х  | Х  | 1  | 0  | Transmitter disabled, transmission ABORTED (status read after an interrupt)  |

| Х               | Х  | Х  | Х  | Х  | 1  | Х  | Х  | Receiver enabled, free to receive                                            |

| Х               | Х  | Х  | 0  | 0  | Х  | Х  | Х  | Currently receiving data                                                     |

| Х               | Х  | Х  | 0  | 1  | Х  | Х  | х  | Receiving IDLE                                                               |

| Х               | Х  | Х  | 1  | 0  | Х  | Х  | Х  | Receiving FLAGS                                                              |

| 0               | 0  | 1  | Х  | Х  | 0  | Х  | х  | Receiver disabled, ABORTED frame received (status read after an interrupt)   |

| 0               | 1  | 0  | Х  | Х  | 0  | Х  | х  | Receiver disabled, OVERRUN frame received (status read after an interrupt)   |

| 1               | 0  | 0  | Х  | Х  | 0  | Х  | Х  | Receiver disabled, TOO LONG frame received (status read after an interrupt)  |

| 1               | 1  | 0  | Х  | Х  | 0  | Х  | Х  | Receiver disabled, VALID frame received (status read after an interrupt)     |

Figure 6: Status interrupt

| Regisler | Function                              | Length<br>(Bits) | Address<br>(Hex) | A3 | A2 | A1 | A0 | R/W |

|----------|---------------------------------------|------------------|------------------|----|----|----|----|-----|

| TFL      | Transmitter Frame Length LS Byte      | 8                | 2                | 0  | 0  | 1  | 0  | R/W |

|          | Transmitter Frame Length MS Byte      | 3                | 3                | 0  | 0  | 1  | 1  | R/W |

| ТА       | Transmitter Address LS Byte           | 8                | 6                | 0  | 1  | 1  | 0  | R/W |

|          | Transmitter Address MS Byte           | 8                | 7                | 0  | 1  | 1  | 1  | R/W |

| S        | Status                                | 8                | 9                | 1  | 0  | 0  | 1  | R   |

| С        | Control                               | 8                | 9                | 1  | 0  | 0  | 1  | W   |

| RFL      | Receiver Frame Length LS Byte         | 8                | A                | 1  | 0  | 1  | 0  | R   |

|          | Receiver Frame Length MS Byte         | 3                | B                | 1  | 0  | 1  | 1  | R   |

| RMFL     | Receiver Maximum Frame Length LS Byte | 8                | C                | 1  | 1  | 0  | 0  | R/W |

|          | Receiver Maximum Frame Length MS Byte | 3                | D                | 1  | 1  | 0  | 1  | R/W |

| RA       | Receiver Address LS Byte              | 8                | E                | 1  | 1  | 1  | 0  | R/W |

|          | Receiver Address MS Byte              | 8                | F                | 1  | 1  | 1  | 1  | R/W |

Figure 7: Register addresses

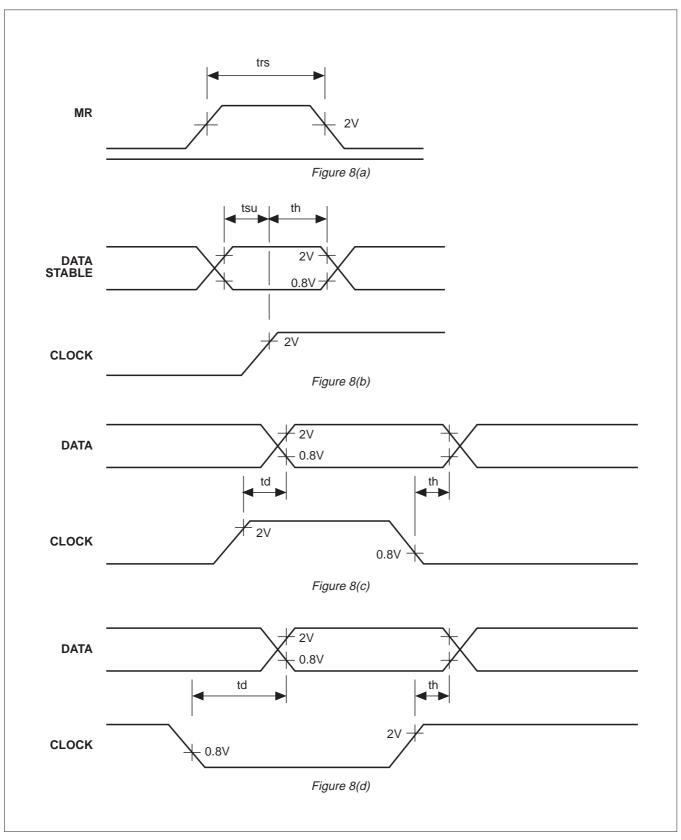

Figure 8: Timing diagram

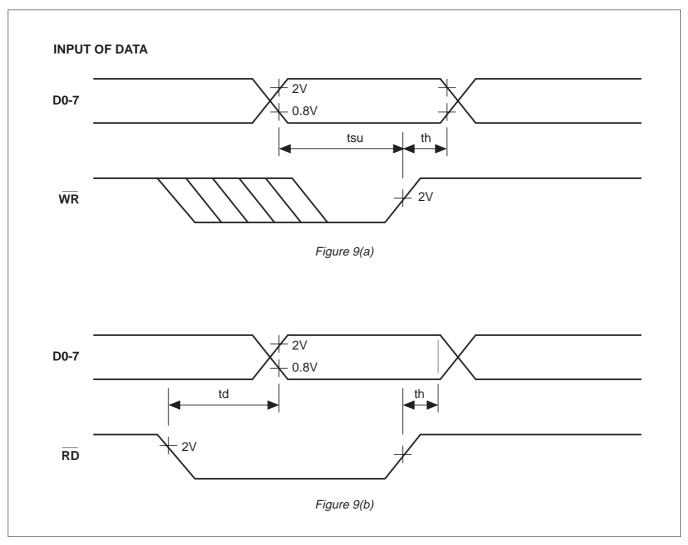

Figure 9: Register timing

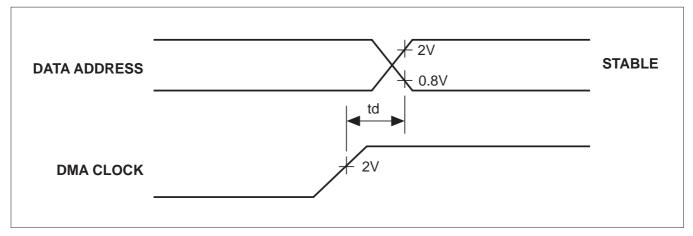

Figure 10: DMA timing

Figure 11: DMA cycle timing

\*During a read cycle, MWR stays high and similarly during a write cycle MRD stays high. All other external signals are the same for both cycles.

## **ABSOLUTE MAXIMUM RATINGS**

| ABSOLUTE MAXIMUM RATING<br>Supply voltage V <sub>CC</sub>                  | -0.3V to 7.0V                  | NOTES                                                                                                                      |

|----------------------------------------------------------------------------|--------------------------------|----------------------------------------------------------------------------------------------------------------------------|

| Input voltage V <sub>IN</sub>                                              | -0.3V to V <sub>CC</sub> +0.3V | 1. Exceeding these ratings may cause permanent damage. Functional operation under these conditions is                      |

| Output voltage V <sub>OUT</sub>                                            | -0.3V to $V_{CC}$ +0.3V        | not implied                                                                                                                |

| Clamp diode current per pin IK<br>(See Note 2)<br>Static discharge voltage | ±18mA                          | <ol><li>Maximum dissipation of 1 second should not be<br/>exceeded, only one output to be tested at any one time</li></ol> |

| Storage temperature Ts<br>Ambient temperature with power                   | -65°C to +150°C                |                                                                                                                            |

| applied T <sub>amb</sub>                                                   | -40°C to +85°C                 |                                                                                                                            |

|                                                                            |                                |                                                                                                                            |

## **ELECTRICAL CHARACTERISTICS**

These characteristics are guaranteed over the following conditions (unless othetwise stated):  $T_{amb} = -40^{\circ}C$  to  $+85^{\circ}C$ ,  $V_{CC} = 5.0V \pm 10\%$ , Ground = 0V

## STATIC CHARACTERISTICS

|                         |                 |                    | Value |      |       | Conditions                         |  |  |

|-------------------------|-----------------|--------------------|-------|------|-------|------------------------------------|--|--|

| Characterislic          | Symbol          | MIn.               | Тур   | Max. | Unlts |                                    |  |  |

| Output high voltage     | V <sub>OH</sub> | V <sub>cc</sub> -2 |       |      | V     | IOH = 0.8mA                        |  |  |

| Output low voltage      | V <sub>OL</sub> |                    |       | 0.4  | V     | I OL = 1 .6mA                      |  |  |

| Input high voltage      | V <sub>IH</sub> | 2.2                |       |      | V     |                                    |  |  |

| Input low voltage       | V <sub>IL</sub> |                    |       | 0.8  | V     |                                    |  |  |

| Input leakage current   | IL              | -10                |       | +10  | μA    | $GND \le V_{IN} \le V_{CC}$        |  |  |

| V <sub>CC</sub> current | I <sub>CC</sub> |                    |       | 1    | mA    | $T_{amb} = -40^{\circ}C$ to +85 °C |  |  |

| Output leakage current  | I <sub>OZ</sub> | -50                |       | +50  | μA    | $GND \le V_{OUT} \le V_{CC}$       |  |  |

| Output S/C current      | I <sub>os</sub> | 15                 |       | 80   | mA    | V <sub>CC</sub> = Max              |  |  |

## SWITCHING CHARACTERISTICS

|                                                  |                 |      | Value |      |       |                |  |

|--------------------------------------------------|-----------------|------|-------|------|-------|----------------|--|

| Characteristic                                   | Symbol          | Min. | Тур.  | Max. | Units | Conditions     |  |

| Maximum DMA clock frequency                      | FDMACK          | 8    |       |      | MHz   |                |  |

| Maximum TX clock frequency                       | FTCK            | 128  |       |      | kHz   |                |  |

| Maximum RX clock frequency                       | FRCK            | 128  |       |      | kHz   |                |  |

| Minimum MR duration                              | t <sub>rs</sub> |      |       |      | ns    | Fig.8(a)       |  |

| RXIP to RCK set-up time                          | t <sub>su</sub> | 0    |       |      | ns    | Fig.8(b)       |  |

| RXIP to RCK hold time                            | t <sub>h</sub>  | 90   |       |      | ns    | Fig.8(b)       |  |

| BAK to DMACK set-up time                         | t <sub>su</sub> | 0    |       |      | ns    | Fig.8(b)       |  |

| BAK to DMACK hold time                           | t <sub>h</sub>  | 25   |       |      | ns    | Fig.8(b)       |  |

| Delay DMA clock to MRD                           | t <sub>d</sub>  |      | 40    | 55   | ns    | Fig.8(c)       |  |

| Delay DMA clock to MWR                           | t <sub>d</sub>  |      | 40    | 55   | ns    | Fig.8(c)       |  |

| Delay RCK ↓ to RINT                              | t <sub>d</sub>  |      | 50    | 110  | ns    | Fig.8(d)       |  |

| Delay, TCK to TINT                               | t <sub>d</sub>  |      | 60    | 90   | ns    | Fig.8(c)       |  |

| Delay, TCK $\Uparrow$ or RCK $\Downarrow$ to BRQ | t <sub>d</sub>  |      | 70    | 90   | ns    | Fig.8(c) & (d) |  |

| Delay, DMACK to AEN                              | t <sub>d</sub>  |      | 40    | 55   | ns    | Fig.8(c)       |  |

| Delay, DMACK to ASB                              | t <sub>d</sub>  |      | 40    | 55   | ns    | Fig.8(c)       |  |

| Delay, TCK to TXoP                               | t <sub>d</sub>  |      | 70    | 115  | ns    | Fig.8(c)       |  |

| Delay, TCK to ToP2                               | t <sub>d</sub>  |      | 60    | 115  | ns    | Fig.8(c)       |  |

| Hold, DMACK to MRD                               | t <sub>h</sub>  |      | 90    | 130  | ns    | Fig.8(d)       |  |

| Hold, DMACK to MWR                               | t <sub>h</sub>  |      | 50    | 75   | ns    | Fig.8(d)       |  |

| Hold, DMACK to BRQ                               | t <sub>h</sub>  |      | 60    |      | ns    | Fig.8(d)       |  |

| Hold, DMACK to AEN                               | t <sub>h</sub>  |      | 30    | 55   | ns    | Fig.8(d)       |  |

| Hold, DMACK to ASB                               | t <sub>h</sub>  |      | 40    | 55   | ns    | Fig.8(d)       |  |

| Data to WR set-up                                | t <sub>su</sub> |      |       |      | ns    | Fig.9(a)       |  |

| WR to data hold                                  | t <sub>h</sub>  |      |       |      | ns    | Fig.9(a)       |  |

| RD to data delay                                 | t <sub>d</sub>  |      | 50    |      | ns    | Fig.9(b)       |  |

| RD to data hold                                  | t <sub>h</sub>  |      |       |      | ns    | Fig.9(b)       |  |

| DMACK to data/address delay                      | t <sub>d</sub>  |      | 60    |      | ns    | Fig.10         |  |

#### HEADQUARTERS OPERATIONS GEC PLESSEY SEMICONDUCTORS Cheney Manor, Swindon,

Cheney Manor, Swindon, Wiltshire SN2 2QW, United Kingdom. Tel: (0793) 518000 Fax: (0793) 518411

#### GEC PLESSEY SEMICONDUCTORS

P.O.Box 660017, 1500 Green Hills Road, Scotts Valley, California 95067-0017, United States of America. Tel (408) 438 2900 Fax: (408) 438 5576

- CUSTOMER SERVICE CENTRES

- FRANCE & BENELUX Les Ulis Cedex Tel: (1) 64 46 23 45 Fax: (1) 64 46 06 07

- GERMANY Munich Tel: (089) 3609 06-0 Fax : (089) 3609 06-55

- ITALY Milan Tel: (02) 66040867 Fax: (02) 66040993

- JAPAN Tokyo Tel: (3) 5276-5501 Fax: (3) 5276-5510

- NORTH AMERICA Integrated Circuits and Microwave Products, Scotts Valley, USA Tel (408) 438 2900 Fax: (408) 438 7023.

- Hybrid Products, Farmingdale, USA Tel (516) 293 8686 Fax: (516) 293 0061.

- SOUTH EAST ASIA Singapore Tel: 2919291 Fax: 2916455

- SWEDEN Johanneshov Tel: 46 8 702 97 70 Fax: 46 8 640 47 36

- UK, EIRE, DENMARK, FINLAND & NORWAY Swindon Tel: (0793) 518510 Fax : (0793) 518582

These are supported by Agents and Distributors in major countries world-wide.

© GEC Plessey Semiconductors 1993 Publication No. DS 3138 Issue No. 2.1 September 1993

This publication is issued to provide information only which (unless agreed by the Company in writing) may not be used, applied or reproduced for any purpose nor form part of any order or contract nor to be regarded as a representation relating to the products or services concerned. No warranty or guarantee express or implied is made regarding the capability, performance or suitability of any product or service. The Company reserves the right to alter without prior knowledge the specification, design or price of any product or service. Information concerning possible methods of use is provided as a guide only and does not constitute any guarantee that such methods of use will be satisfactory in a specific piece of equipment. It is the user's responsibility to fully determine the performance and suitability of any equipment using such information and to ensure that such methods of use is up to date and has not been superseded. These products are not suitable for use in any medical products products any result in significant injury or death to the user. All products and materials are sold and services provided subject to the Company's conditions of sale, which are available on request.

# For more information about all Zarlink products visit our Web Site at

# www.zarlink.com

Information relating to products and services furnished herein by Zarlink Semiconductor Inc. trading as Zarlink Semiconductor or its subsidiaries (collectively "Zarlink") is believed to be reliable. However, Zarlink assumes no liability for errors that may appear in this publication, or for liability otherwise arising from the application or use of any such information, product or service or for any infringement of patents or other intellectual property rights owned by third parties which may result from such application or use. Neither the supply of such information or purchase of product or service conveys any license, either express or implied, under patents or other intellectual property rights owned by Zarlink or licensed from third parties by Zarlink, whatsoever. Purchasers of products are also hereby notified that the use of product in certain ways or in combination with Zarlink, or non-Zarlink furnished goods or services may infringe patents or other intellectual property rights owned by Zarlink owned by Zarlink.

This publication is issued to provide information only and (unless agreed by Zarlink in writing) may not be used, applied or reproduced for any purpose nor form part of any order or contract nor to be regarded as a representation relating to the products or services concerned. The products, their specifications, services and other information appearing in this publication are subject to change by Zarlink without notice. No warranty or guarantee express or implied is made regarding the capability, performance or suitability of any product or service. Information concerning possible methods of use is provided as a guide only and does not constitute any guarantee that such methods of use will be satisfactory in a specific piece of equipment. It is the user's responsibility to fully determine the performance and suitability of any equipment using such information and to ensure that any publication or data used is up to date and has not been superseded. Manufacturing does not necessarily include testing of all functions or parameters. These products are not suitable for use in any medical products whose failure to perform may result in significant injury or death to the user. All products and materials are sold and services provided subject to Zarlink's conditions of sale which are available on request.

Purchase of Zarlink s I<sup>2</sup>C components conveys a licence under the Philips I<sup>2</sup>C Patent rights to use these components in and I<sup>2</sup>C System, provided that the system conforms to the I<sup>2</sup>C Standard Specification as defined by Philips.

Zarlink and the Zarlink Semiconductor logo are trademarks of Zarlink Semiconductor Inc.

Copyright 2001, Zarlink Semiconductor Inc. All Rights Reserved.

## TECHNICAL DOCUMENTATION - NOT FOR RESALE